232层3D闪存芯片来了:单片容量2TB,传输速度提高50%

美光首发

Pine 发自 凹非寺

量子位 | 公众号 QbitAI

232层的3D闪存芯片来了,数据传输速率提高50%,容量可达2TB。

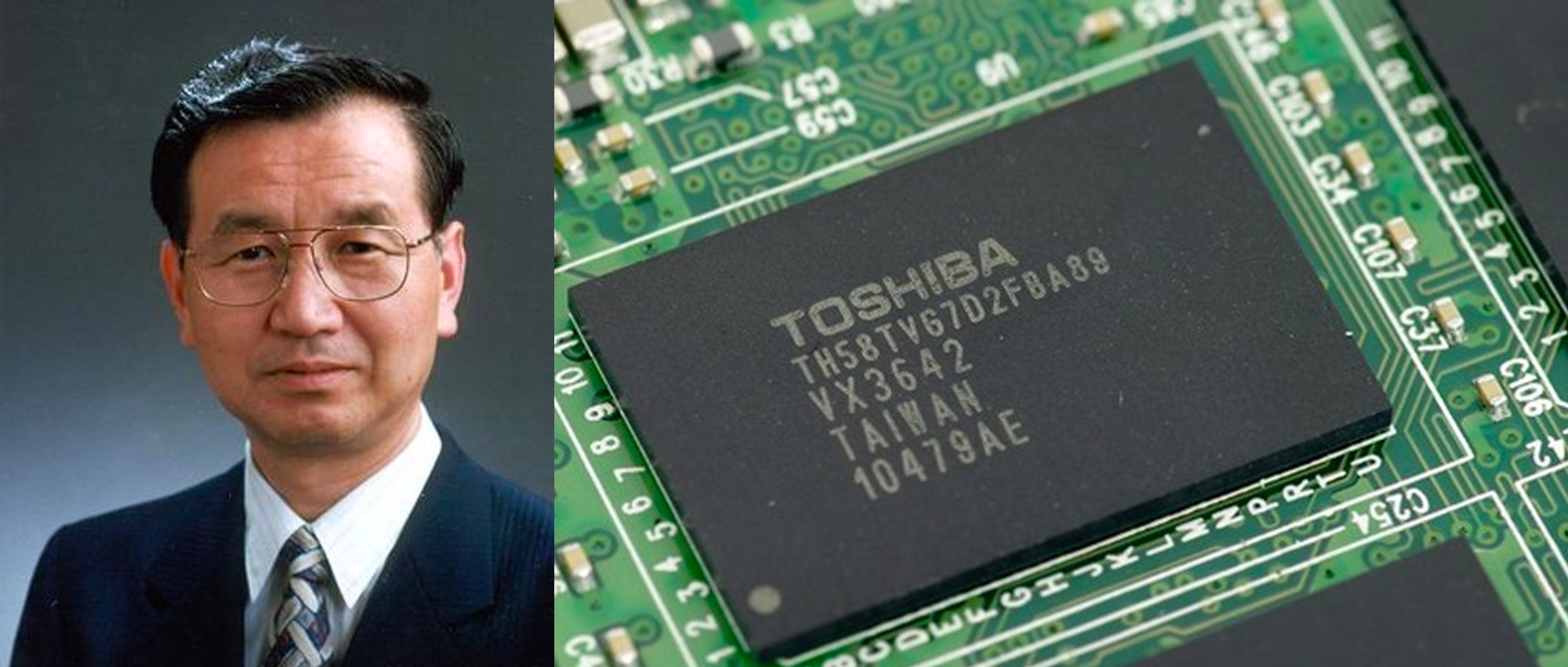

美光继上次抢先推出176层3D NAND后,近日又率先推出全球首款232层NAND。

△图源美光科技

说起来,跟NAND层数较劲这事儿,并不是美光一家在做。

比如美光的老对手三星,相关研究中心也聚焦在层数上:此前,三星曾抢先业界公布了第八代V-NAND的细节,堆栈层数超过200层。

所以这样“堆高高”,究竟能给芯片性能带来多大的提升?

堆栈层数就像盖楼房

层数越高,NAND闪存可具有的容量就越大。

可以做这样一个简单的比喻:

在一个人满为患的城市,这里的房地产价格昂贵,向外扩展成本很大,唯一的办法是通过增加楼层以支持不断增长的人口,这里的楼层就相当于NAND层。

同样的,停车场和一些基础设施主要位于建筑物下方,以提高空间效率,这相当于最底下的CMOS层。

将NAND的位单元阵列堆叠到更多层中,可在每平方毫米硅片上提供更多存储位,从而实现更高的密度和更低的成本。

3D NAND把解决思路从单纯提高制程工艺转变为堆叠多层,成功解决了平面NAND在增加容量的同时性能降低的问题,实现容量、速度、能效及可靠性等全方位提升。

△图源美光科技

和三星等其他竞争芯片相比,美光新的技术将每单位面积存储的比特密度提高了一倍,每平方毫米封装14.6Gb。

它的1TB芯片被捆绑在2TB的封装中,每个封装的边长都不超过一厘米,可以存储大约两周时长的4K视频。

此外,美光还对芯片的最底层进行了改进,最底下的CMOS层由逻辑和其他电路组成,这些电路负责控制读写操作以及尽可能快速有效地在芯片内外获取数据。

美光优化了其数据传输路径,降低芯片输入和输出的电容,将数据传输速率提高了50%,达到2.4Gb/s。

层数的较量

自从NAND 闪存进入3D时代,堆栈层数犹如摩天大楼一样越来越高,从最初的24/32层一路堆到了现在的176层甚至232层。

层数的较量是整个行业的竞争,三星、美光、SK海力士等企业都致力于层数的突破。

三星是NAND闪存的龙头企业,3D NAND就源于三星。

2013年,三星设计了一种垂直堆叠单元的方法,它将单元集中在单个楼层(类似高层公寓)上,这也是全球首个3D单元结构“V-NAND”,当年可以实现24层堆叠。

此后,三星不断更新技术和扩增产业线,10年间推出了7代产品,以维护自己在NAND闪存市场的地位。

2020年,三星推出了176层的第七代“V-NAND”,它采用了“双堆栈”技术,不是一次性蚀刻所有层,而是将它们分成两部分,然后一层一层堆叠。

因此,第七代V-NAND相较于与第六代的100层,其单元体积减少了35%,它可以在不增加高度的情况下将层数增加到176,同时还可以降低功耗,使效率提高16%。

不过,虽然三星曾抢先公布了第八代V-NAND的细节,称其堆栈层数会超过200层,但这回率先量产200+层闪存的却是美光。

值得一提的是,在此次美光发布的232层3D闪存芯片中,NAND的堆栈技术并不是首创,而是与三星第七代一样采用“双堆栈”技术。

也就是说,将232层分成两部分,每个部分116层,这些层的堆叠是从一个深而窄的孔开始,通过导体和绝缘体的交替层蚀刻。

然后用材料填充孔并加工形成器件的比特存储部分。蚀刻和填充穿过所有这些层的孔的能力是该技术的关键限制。

△图注:图源美光科技

目前,国产芯片企业长江存储的第三代QLC 3D NAND闪存实现了128层堆叠。

对于层数的较量,网友也抱有很乐观的态度:

增加层数几乎不会带来新的问题。

参考链接:

[1] https://spectrum.ieee.org/micron-is-first-to-deliver-3d-flash-chips-with-more-than-200-layers

[2] https://news.ycombinator.com/item?id=32243862

[3] https://ee.ofweek.com/2021-12/ART-8320315-8110-30538953.html

— 完 —

- GPT-5不能停!吴恩达田渊栋反对千人联名,OpenAI CEO也发声了2023-03-30

- ChatGPT标注数据比人类便宜20倍,80%任务上占优势 | 苏黎世大学2023-03-29

- 马斯克嘲讽比尔盖茨不懂AI/ 苹果收购AI视频公司/ 壁仞GPU联创出走…今日更多新鲜事在此2023-03-28

- GPT-4老板:AI可能会杀死人类,已经出现我们无法解释的推理能力2023-03-28