湖南大学让晶体管小至3纳米,沟道长度仅一层原子 | Nature子刊

「亚纳米晶体管」关键技术

月石一 发自 凹非寺

量子位 报道 | 公众号 QbitAI

湖南大学团队成功实现了超短沟道的垂直场效应晶体管(VFET)。

沟道长度可以缩短到0.65nm,几乎只有一个原子的大小。

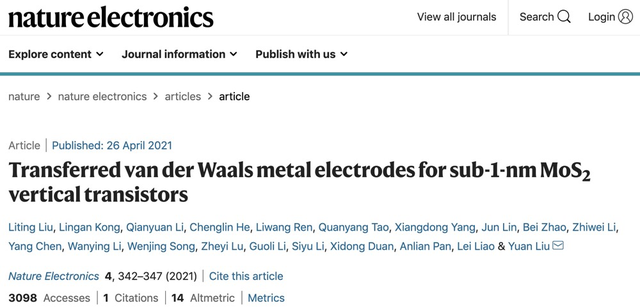

这项研究的论文登上了《Nature Electronics》。

要知道,受短沟道效应、传统高能金属沉积技术、高精度光刻技术等限制,想把沟道长度降低到10nm以下是非常困难的。

现在,这项研究为芯片性能提升提供了新思路。

范德华金属电极集成

为什么这么说?

首先要从MOS管的全称——金属氧化物半导体场效应晶体管(MOSFET)说起。

“N型”与“P型” 是根据极性划分的两种半导体,它们可以单向导电。

就NPN型MOS管来说,由于单向导电性的原因,NPN之间存在两个PN结,因此无法导通。

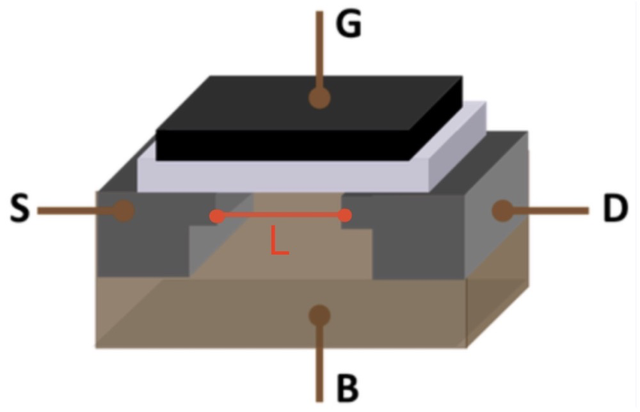

于是,需要在P区上方依次放上二氧化硅绝缘层和金属板,这就是栅极(G),两个N型半导体则分别对应漏极(D)和源极(S)。

△图源:wikipedia

在栅极接电后,它能够将P区中的电子吸引到两块N型半导体之间,从而在源极和漏极之间形成了沟道。

在宽度不变的条件下,沟道长度(L)越短,开关的速度越快。

如今,新研究让这一数值小至0.65nm,这无疑是一项重大突破。

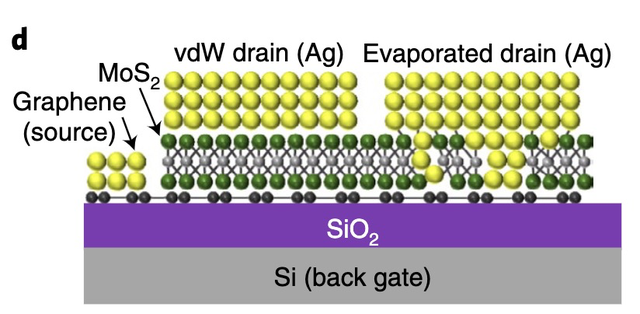

简单来说,研究人员采用了范德华(vdW)金属电极集成方法,以二硫化钼(MoS2)作为半导体沟道的薄层甚至单原子层。

然后,将预制备的金属电极物理层,压到二硫化钼沟道的顶部,最终得到了MoS2 VFET。

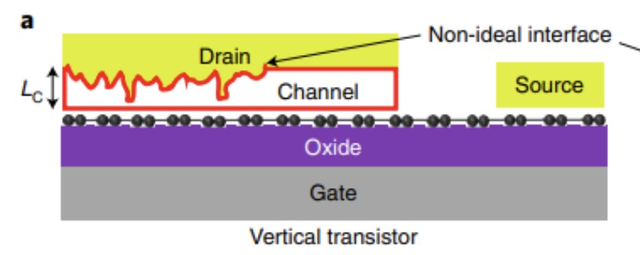

结构横截面是这样的:

与传统的金属沉积技术相比,这种新方法能保留二维半导体的晶格结构和固有特性,从而形成原子级别平整的金属-半导体界面,减少隧穿电流。

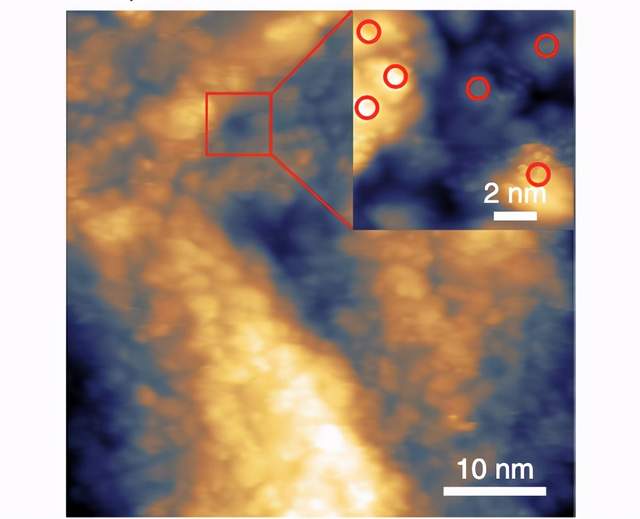

通过范德华金属-半导体界面的隧穿光谱图像,可以观察到原子级分辨率的均匀二维晶格稳定结构。

直接沉积的金属-半导体界面的隧穿光谱图像,显示出明显的晶格畸变和高导电路径(红色圆圈)。

芯片苦「亚纳米」久矣

半导体产业一直遵循的“摩尔定律”指出:

集成电路上可容纳的晶体管数目,约每隔18个月(另一说法为2年)便会增加一倍;微处理器的性能提高一倍,或价格下降一半。

为满足高性能微缩器件的需求,晶体管的尺寸不断缩小,随之而来也出现了一系列问题:迁移率降低、漏电流增大、隧穿电流增大、功耗增加等。

这些都是严重的短沟道效应,这说明平行晶体管的导电沟道长度过短,微缩方法已经逼近了物理极限。

△图中L为沟道长度

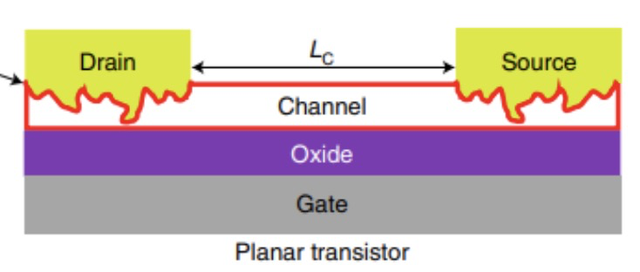

与之不同的垂直晶体管开始受到关注,其纵向的结构具有天然的短沟道特性,半导体沟道位于底电极与顶部电极之间,沟道长度仅取决于材料厚度。

但是从图中可以看出,在纵向结构中,接触界面(红色线条)直接关系到沟道长度,从而影响电学性能。

也就是说,对垂直晶体管进行微缩时,必须要考虑对金属-半导体间接触界面的影响。

随着物理极限的逼近,芯片性能已经不能单纯地依赖晶体管数量,曾经的“业界铁律”可能要失效了,半导体行业逐渐进入“后摩尔时代”。

现在,研究团队使用范德华金属集成法,成功实现了有效沟道长度小于1nm的垂直场效应晶体管。

经过测试,研究人员发现,在垂直晶体管沟道长度为0.65nm和3.6nm的情况下,仍可以实现26和1000的开关比,开关比性能提升了两个数量级。

虽然超短沟道使得开关比有所下降,但是低温电学测试表明,这种晶体管仍保持了电子发射为主导的特性。

此外,这种方法还具有普适性。研究人员将这种方法用于二硒化钨、二硫化钨等层状半导体,都实现了3nm以下厚度的垂直场效应晶体管。

以此项研究为基础,有望进一步缩小真正的物理沟道长度,摆脱高精度光刻技术和刻蚀技术的限制。

不仅为生产亚3nm级别垂直晶体管带来了希望,还可用于提高范德华异质结器件界面的工艺水平。

论文地址:

https://www.nature.com/articles/s41928-021-00566-0

参考链接:

[1]http://spe.hnu.edu.cn/info/1081/5942.htm

[2]https://techxplore.com/news/2021-06-molybdenum-disulfide-vertical-transistors-channel.html

[3]https://en.wikipedia.org/wiki/MOSFET#Structure_and_channel_formation

- 魔改宜家灯泡当主机,玩转《毁灭战士》无压力!网友:远超我家第一台电脑2021-06-17

- 苹果为了不让AirTag被用来跟踪,将推出一个安卓应用2021-06-17

- 中国程序员开发的远程桌面火了!Mac可用,只有9MB,支持自建中继器2021-06-17

- 亚马逊员工流动率150%,每8个月相当于“大换血”,网友:贝佐斯不知足2021-06-16